výrobky Kategórie

- FM vysielač

- 0-50w 50w-1000w 2kw-10kw 10kw +

- televízny vysielač

- 0-50w 50-1kw 2kw-10kw

- FM anténa

- TV anténa

- anténa príslušenstvo

- kábel konektor power Splitter Dummy Load

- RF Transistor

- Zdroj

- audio Príslušenstvo

- DTV Front End Zariadenie

- link System

- STL systém Link systém Mikrovlnná rúra

- FM rádio

- power Meter

- Ostatné produkty

- Špeciálne pre Coronavirus

produkty Značky

Fmuser Sites

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> afrikánčina

- sq.fmuser.net -> albánsky

- ar.fmuser.net -> arabčina

- hy.fmuser.net -> Arménsky

- az.fmuser.net -> azerbajdžanský

- eu.fmuser.net -> baskičtina

- be.fmuser.net -> bieloruský

- bg.fmuser.net -> Bulgarian

- ca.fmuser.net -> katalánčina

- zh-CN.fmuser.net -> čínština (zjednodušená)

- zh-TW.fmuser.net -> čínština (tradičná)

- hr.fmuser.net -> chorvátčina

- cs.fmuser.net -> čeština

- da.fmuser.net -> dánčina

- nl.fmuser.net -> Dutch

- et.fmuser.net -> estónčina

- tl.fmuser.net -> filipínsky

- fi.fmuser.net -> fínčina

- fr.fmuser.net -> French

- gl.fmuser.net -> galícijčina

- ka.fmuser.net -> gruzínsky

- de.fmuser.net -> nemčina

- el.fmuser.net -> Greek

- ht.fmuser.net -> haitská kreolčina

- iw.fmuser.net -> hebrejčina

- hi.fmuser.net -> hindčina

- hu.fmuser.net -> Hungarian

- is.fmuser.net -> islandský

- id.fmuser.net -> indonézština

- ga.fmuser.net -> írsky

- it.fmuser.net -> Italian

- ja.fmuser.net -> japončina

- ko.fmuser.net -> kórejčina

- lv.fmuser.net -> lotyšský

- lt.fmuser.net -> litovčina

- mk.fmuser.net -> macedónsky

- ms.fmuser.net -> malajčina

- mt.fmuser.net -> maltčina

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> perzský

- pl.fmuser.net -> poľština

- pt.fmuser.net -> portugalčina

- ro.fmuser.net -> rumunčina

- ru.fmuser.net -> ruština

- sr.fmuser.net -> srbčina

- sk.fmuser.net -> slovenčina

- sl.fmuser.net -> slovinčina

- es.fmuser.net -> španielčina

- sw.fmuser.net -> svahilčina

- sv.fmuser.net -> švédčina

- th.fmuser.net -> Thai

- tr.fmuser.net -> turečtina

- uk.fmuser.net -> ukrajinčina

- ur.fmuser.net -> urdčina

- vi.fmuser.net -> Vietnamese

- cy.fmuser.net -> waleština

- yi.fmuser.net -> jidiš

Čo je polovica sčítačky: Schéma zapojenia a jej aplikácie

Date:2021/10/18 21:55:58 Hits:

Half Adder je druh základného digitálneho obvodu. Predtým sa v analógových obvodoch vykonávali rôzne operácie. Po objave digitálnej elektroniky sa v nej vykonávajú podobné operácie. Digitálne systémy sú považované za účinné a spoľahlivé. Medzi rôznymi operáciami je jednou z najvýznamnejších operácií aritmetika. Obsahuje sčítanie, odčítanie, násobenie a delenie. Už je však známe, že to môže byť počítač, akékoľvek elektronické zariadenie ako kalkulačka môže vykonávať matematické operácie. Tieto operácie, ktoré sa vykonávajú, pozostávajú z binárnych hodnôt. Je to možné prítomnosťou určitých obvodov. Tieto obvody sa označujú ako binárne sčítače a odčítače. Tento typ obvodov je určený aj pre binárne kódy, kódy Excess-3 a ďalšie kódy. Ďalšie binárne adéry sú rozdelené do dvoch typov. Sú to: polovičná sčítačka a plná sčítačka Proces pridávania je denárny, jediným rozdielom je zvolený číselný systém. V systéme binárnych číslovaní existuje iba 0 a 1. Váha čísla je úplne založená na pozíciách binárnych číslic. Medzi týmito 1 a 0 sa 1 považuje za najväčšiu číslicu a 0 za menšiu. Blokový diagram tejto sčítačky je Schéma polovičnej sčítačky Polovičná sčítačka sa skladá z dvoch vstupov a produkuje dva výstupy. Je považovaný za najjednoduchší digitálny obvod. Vstupmi do tohto obvodu sú bity, na ktorých sa má pridanie vykonať. Získané výstupy sú súčet a prenos.

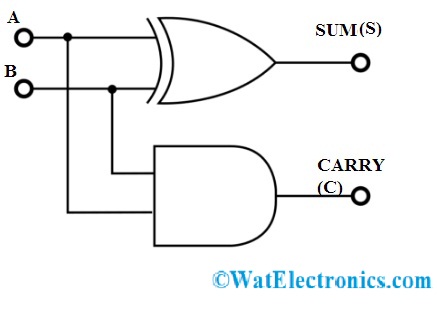

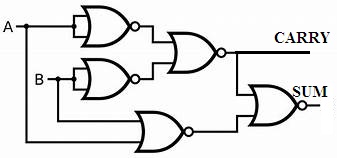

Schéma polovičnej sčítačky Polovičná sčítačka sa skladá z dvoch vstupov a produkuje dva výstupy. Je považovaný za najjednoduchší digitálny obvod. Vstupmi do tohto obvodu sú bity, na ktorých sa má pridanie vykonať. Získané výstupy sú súčet a prenos.  Polovičný sčítač Obvod tohto zmije sa skladá z dvoch brán. Sú to brány AND a XOR. Aplikované vstupy sú rovnaké pre obe brány prítomné v obvode. Ale výstup je odobratý z každej brány. Výstup brány XOR sa označuje ako SUM a výstup AND je známy ako CARRY. Polovica sčítačky Pravdivá tabuľka Na získanie vzťahu získaného výstupu k použitému vstupu je možné analyzovať tabuľku známu ako Pravdivá tabuľka.

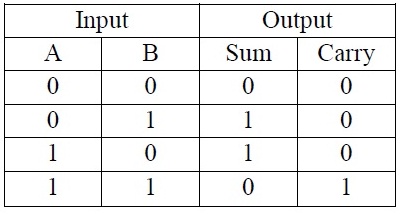

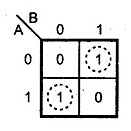

Polovičný sčítač Obvod tohto zmije sa skladá z dvoch brán. Sú to brány AND a XOR. Aplikované vstupy sú rovnaké pre obe brány prítomné v obvode. Ale výstup je odobratý z každej brány. Výstup brány XOR sa označuje ako SUM a výstup AND je známy ako CARRY. Polovica sčítačky Pravdivá tabuľka Na získanie vzťahu získaného výstupu k použitému vstupu je možné analyzovať tabuľku známu ako Pravdivá tabuľka. Tabuľka pravdy polovičnej sčítačky Z vyššie uvedenej tabuľky pravdy sú zrejmé nasledujúce body: Ak A = 0, B = 0, obidva použité vstupy sú 0. Potom sú obidva výstupy SUM a CARRY 0. Medzi dvoma zadanými vstupmi, ak niekto vstup je 1, potom SUMA bude b e1, ale VYKONANIE je 0. Ak sú obidva vstupy 1, potom SÚČET sa bude rovnať 0 a NOSIŤ sa bude rovnať 1. Na základe použitých vstupov pokračuje polovičný sčítač v operácii Rovnicu Rovnicu pre tento typ obvodov je možné realizovať pomocou pojmov súčet produktov (SOP) a súčin súčtov (POS). Booleovská rovnica pre tento typ obvodov určuje vzťah medzi aplikovanými vstupmi a získanými výstupmi. Na určenie rovnice sú k-mapy nakreslené na základe hodnôt tabuľky pravdy. Pozostáva z dvoch rovníc, pretože sú v ňom použité dve logické brány. K-mapa prenosu je

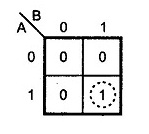

Tabuľka pravdy polovičnej sčítačky Z vyššie uvedenej tabuľky pravdy sú zrejmé nasledujúce body: Ak A = 0, B = 0, obidva použité vstupy sú 0. Potom sú obidva výstupy SUM a CARRY 0. Medzi dvoma zadanými vstupmi, ak niekto vstup je 1, potom SUMA bude b e1, ale VYKONANIE je 0. Ak sú obidva vstupy 1, potom SÚČET sa bude rovnať 0 a NOSIŤ sa bude rovnať 1. Na základe použitých vstupov pokračuje polovičný sčítač v operácii Rovnicu Rovnicu pre tento typ obvodov je možné realizovať pomocou pojmov súčet produktov (SOP) a súčin súčtov (POS). Booleovská rovnica pre tento typ obvodov určuje vzťah medzi aplikovanými vstupmi a získanými výstupmi. Na určenie rovnice sú k-mapy nakreslené na základe hodnôt tabuľky pravdy. Pozostáva z dvoch rovníc, pretože sú v ňom použité dve logické brány. K-mapa prenosu je  K-Mapa A brána Výstupná rovnica CARRY sa získa z brány AND. C = A. B. Booleovský výraz pre SUM je realizovaný pomocou formulára SOP. K-mapa pre SUM je teda

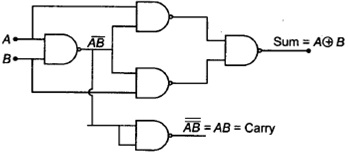

K-Mapa A brána Výstupná rovnica CARRY sa získa z brány AND. C = A. B. Booleovský výraz pre SUM je realizovaný pomocou formulára SOP. K-mapa pre SUM je teda K-mapa pre súčet (XOR) Stanovená rovnica je S = A⊕ BAplikácie Aplikácia tejto základnej sčítačky je nasledovná Na vykonávanie adícií na binárnych bitoch uprednostňuje tento sčítací obvod aritmetická a logická jednotka prítomná v počítači. Kombinácia polovičných obvodov sčítačky k vytvoreniu obvodu Full Adder. Tieto logické obvody sú pri konštrukcii kalkulačiek uprednostňované. Na výpočet adries a tabuliek sa uprednostňujú tieto obvody. Namiesto jediného doplnku sú tieto obvody schopné zvládnuť rôzne aplikácie v digitálnych obvodoch. Ďalej sa to stáva jadrom digitálnej elektroniky. Kód VHDL Kód VHDL pre obvod Half Adder islibrary ieee; použite ieee.std_logic_1164.all; entita half_adder isport (a, b: v bite; súčet, vykonanie: out bit); koniec Half_adder ; údaje o architektúre half_adder isbeginsum <= a xor b; carry <= a a b; end data; FAQs1. Čo rozumiete pod pojmom Adder? Digitálne obvody, ktorých jediným účelom je vykonávať sčítanie, sú známe ako sčítače. Toto sú hlavné súčasti ALU. Sčítače fungujú okrem rôznych formátov čísel. Výstupy sčítačov sú súčet a prenos.2. Aké sú obmedzenia polovičnej sčítačky? Prenosový bit generovaný z predchádzajúceho bitu nemožno pridať, je obmedzením tohto sčítača. Ak chcete vykonať sčítanie pre viac bitov, tieto obvody nemožno uprednostniť. Ako implementovať polovičnú sčítačku pomocou brány NOR? Implementáciu tohto typu sčítačky je možné vykonať aj pomocou brány NOR. Toto je ďalšia univerzálna brána.

K-mapa pre súčet (XOR) Stanovená rovnica je S = A⊕ BAplikácie Aplikácia tejto základnej sčítačky je nasledovná Na vykonávanie adícií na binárnych bitoch uprednostňuje tento sčítací obvod aritmetická a logická jednotka prítomná v počítači. Kombinácia polovičných obvodov sčítačky k vytvoreniu obvodu Full Adder. Tieto logické obvody sú pri konštrukcii kalkulačiek uprednostňované. Na výpočet adries a tabuliek sa uprednostňujú tieto obvody. Namiesto jediného doplnku sú tieto obvody schopné zvládnuť rôzne aplikácie v digitálnych obvodoch. Ďalej sa to stáva jadrom digitálnej elektroniky. Kód VHDL Kód VHDL pre obvod Half Adder islibrary ieee; použite ieee.std_logic_1164.all; entita half_adder isport (a, b: v bite; súčet, vykonanie: out bit); koniec Half_adder ; údaje o architektúre half_adder isbeginsum <= a xor b; carry <= a a b; end data; FAQs1. Čo rozumiete pod pojmom Adder? Digitálne obvody, ktorých jediným účelom je vykonávať sčítanie, sú známe ako sčítače. Toto sú hlavné súčasti ALU. Sčítače fungujú okrem rôznych formátov čísel. Výstupy sčítačov sú súčet a prenos.2. Aké sú obmedzenia polovičnej sčítačky? Prenosový bit generovaný z predchádzajúceho bitu nemožno pridať, je obmedzením tohto sčítača. Ak chcete vykonať sčítanie pre viac bitov, tieto obvody nemožno uprednostniť. Ako implementovať polovičnú sčítačku pomocou brány NOR? Implementáciu tohto typu sčítačky je možné vykonať aj pomocou brány NOR. Toto je ďalšia univerzálna brána. Polovičná sčítačka používajúca brány NOR4. Ako implementovať polovičnú výbavu pomocou brány NAND? Brána NAND je jedným z druhov univerzálnych brán. To naznačuje, že pomocou brán NAND je možný akýkoľvek druh navrhovania obvodov.

Polovičná sčítačka používajúca brány NOR4. Ako implementovať polovičnú výbavu pomocou brány NAND? Brána NAND je jedným z druhov univerzálnych brán. To naznačuje, že pomocou brán NAND je možný akýkoľvek druh navrhovania obvodov. Polovičná sčítačka Z vyššie uvedeného obvodu možno prenosový výkon generovať aplikáciou výstupu jednej brány NAND na vstup ako inej brány NAND. To nie je nič iné, ako známe výstupu získanému z brány AND. Výstupnú rovnicu SUM je možné generovať aplikáciou výstupu počiatočnej brány NAND spolu s jednotlivými vstupmi A a B na ďalšie brány NAND. Nakoniec sa výstupy získané týmito bránami NAND opäť aplikujú na bránu. Preto je generovaný výstup pre SUM. Preto je možné základnú sčítačku v digitálnom obvode navrhnúť pomocou rôznych logických brán. Sčítanie viacerých bitov sa však komplikuje a považuje sa za obmedzenie polovičnej sčítačky. Môžete popísať, ktorý IC sa používa na prírastkovú operáciu v akýchkoľvek praktických počítadlách?

Polovičná sčítačka Z vyššie uvedeného obvodu možno prenosový výkon generovať aplikáciou výstupu jednej brány NAND na vstup ako inej brány NAND. To nie je nič iné, ako známe výstupu získanému z brány AND. Výstupnú rovnicu SUM je možné generovať aplikáciou výstupu počiatočnej brány NAND spolu s jednotlivými vstupmi A a B na ďalšie brány NAND. Nakoniec sa výstupy získané týmito bránami NAND opäť aplikujú na bránu. Preto je generovaný výstup pre SUM. Preto je možné základnú sčítačku v digitálnom obvode navrhnúť pomocou rôznych logických brán. Sčítanie viacerých bitov sa však komplikuje a považuje sa za obmedzenie polovičnej sčítačky. Môžete popísať, ktorý IC sa používa na prírastkovú operáciu v akýchkoľvek praktických počítadlách?

Predchádzajúce:Čo je Gunnova dióda: Konštrukcia a jej fungovanie

Zanechajte správu

zoznam správ

Komentáre Loading ...